计算机组成原理

更新: 1/6/2025 字数: 0 字 时长: 0 分钟

- 考试题型:四道大题

- 时间:10:40 - 12:40

- 地点:西楼 - 514

- 监考老师:张瑞娟、王晓辉

什么是计算机?

- 计算机是一种能够按照事先存储的程序,自动、高速、准确地对相关信息进行处理的电子设备。

计算机的关键特征?

- 关键特征:包括存储程序和程序控制。

- 存储程序:就是将解题的步骤编制成程序,然后将程序和运行程序所需要的数据以二进制的形式存放到存储器中,方便执行。

- 程序控制:计算机中的控制器逐条取出存储器中的指令并按顺序执行,控制各功能部件进行相应的操作,完成数据的加工处理。

举出三种不同的计算机?

- 巨型计算机:运算速度快,存储容量大,功能强大

- 微型计算机:体积小,操作简单,通用性强

- 嵌入式计算机:专用性,体积小,功耗低,可靠性高

- 超级计算机:运算速度起快,存诸容量大,功能强大

冯·诺依曼体系结构

- 包括运算器、控制器、存储器、输入设备、输出设备五大部分

- 存储器:存放程序和数据

- 运算器:用于信息加工处理的部件,对数据进行算术运算和逻辑运算

- 控制器:指挥和协调各部件工作

- 硬盘:存储海量信息,不丢失

- 输入设备:将信息输入计算机的外部设备(键盘、鼠标)

- 输出设备:呈现对数据处理的结果(打印机、显示器)

各部件之间有什么交互关系?

- CPU 通过主板连接内存,从内存中提取数据和指令,经 I/O 接口进行输出或者流回

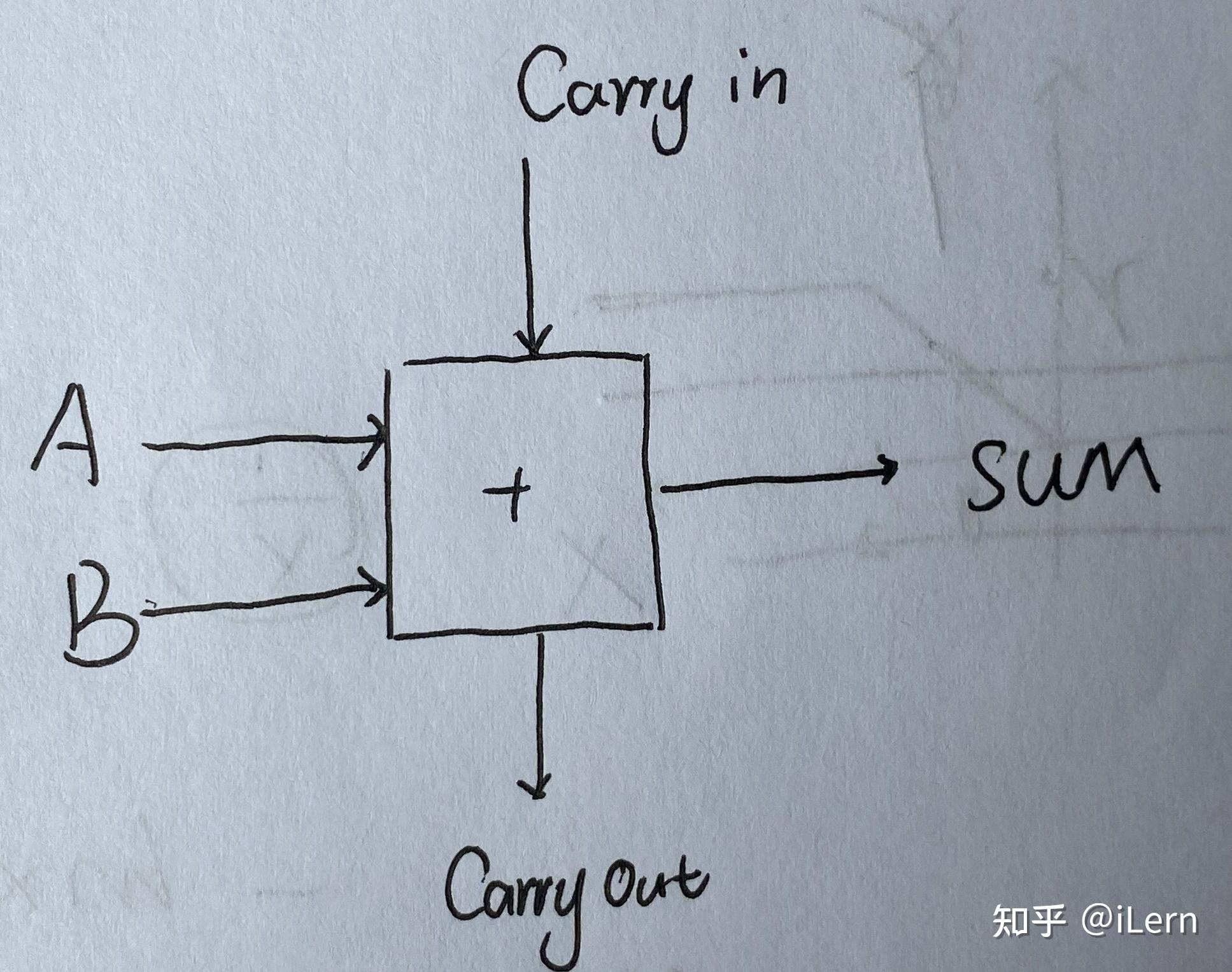

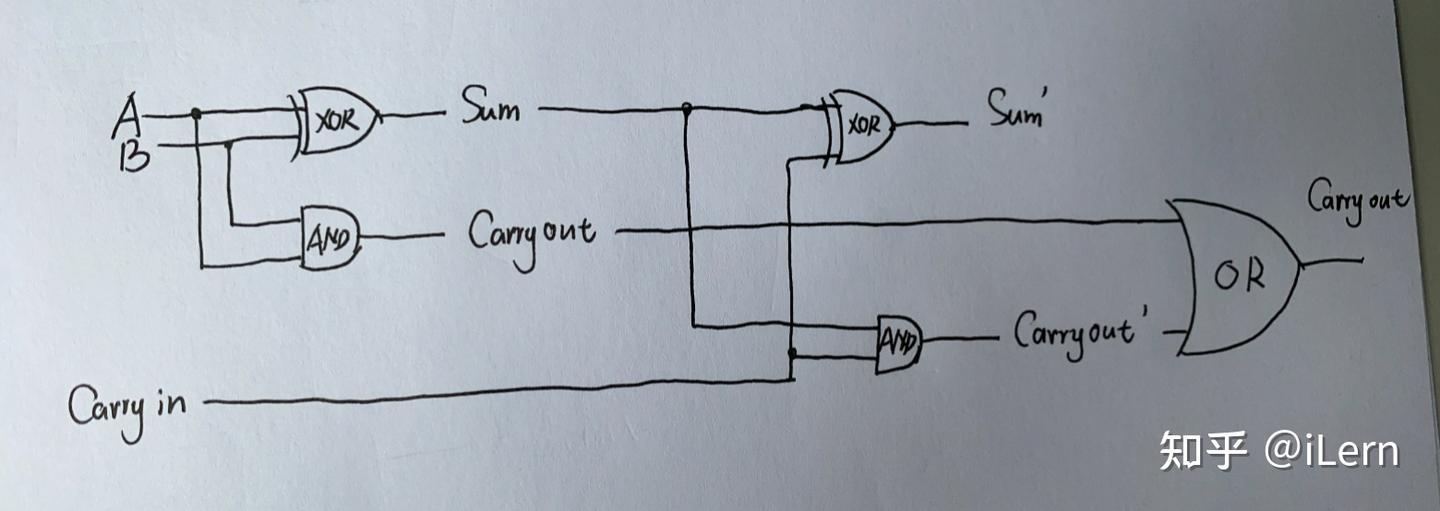

全加器的逻辑框图

怎么提高总线的传输率?

增加总线宽度,提高总线时钟频率,采用先进的传输协议

- 输入没备:负责将数据、文字、图像、声音、电信号等转换成计算机可以识别的二进制信息

- 输出没备:负责将计算机处理结果转换成数字、文字、图形、声音、电信号

cache 缓存

命中率:

为某程序运行期间命中 cache 的次数 为从主存中访问信息的次数

缺失率:

表示命中访问时间 表示缺失访问时间

访问效率:

表示主存与 cache 访问时间的倍数

程序计数器

- 取指令(IF):负责从指令存储器中取出指令

- 指令译码(ID):操作控制器对指令字进行译码,同时从寄存器堆中取操作数

- 指令执行(EX):执行运算操作或计算地址

- 访存(MEM):对存储器进行读写操作

- 写回(WB):将指执行结果写回寄存器堆

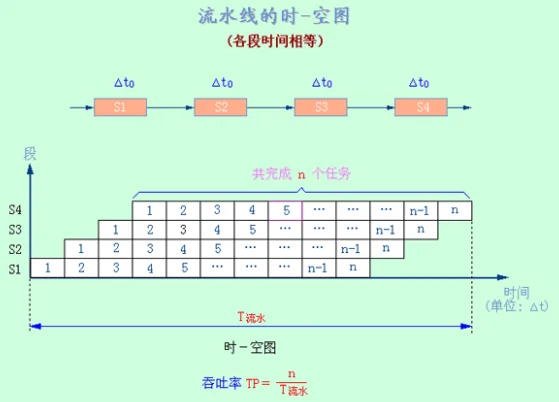

吞吐率:

加速此:

效率:

例 4.1

设计算机字长为 64 位,存储器容量为 128MW,采用模数为 8 的存储器交叉方式进行组织,存储周期

- 顺序方式下,连续读 8 个字所需要的时间

- 则顺序方式下存储器带宽

- 交叉方式下,连续读 8 个字所需要的时间

- 则交叉方式下存储器带宽

例 8.2

若异步串行传输的信息帧由 1 个起始位、7 个数据位、1 个奇偶校验位和 1 个停止位等 10 个数位构成,线路每秒传送 120 个字符,分别计算波特率和数传率。

例 8.4

假定某总线的时钟频率为 1GHz,每次总线传输需要 1 个时钟周期,总线的数据总线宽度为 64 位,存储器的存储周期为两个时钟周期,求同步方式下 CPU 从该存储器中读一个存储字时总线的数据传输速率为多少。

则同步方式下存储器读操作步骤及所需的时间分别如下

(1)寻址阶段:需要一个总线周期时间1ns

(2)存储器读数据并传输到数据总线:需要一个存储周期2ns

(3)CPU从数据总线取走数据:需要一个总线周期 1ns

则同步方式下从主存读一个存储字的总时间